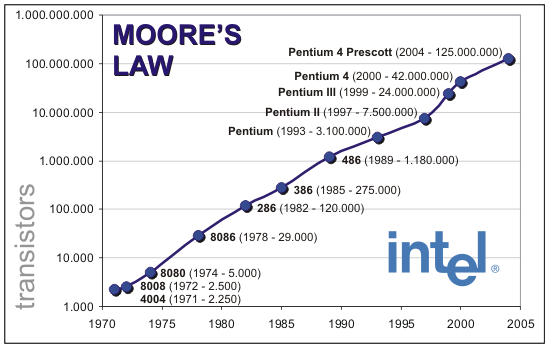

Moore's Law has been valid since it was first formulated in 1965

After nearly 40 years, Moore’s Law, an observation about the evolution of computers, made back in 1965 by Intel co-founder Gordon Moore, is coming to an end. We have been hearing predictions about Moore’s Law ending around 2020 at the 7nm node, where manufacturing difficulties are said to become too challenging, but the reality of the situation is actually different.

Problem with such hypothesis is that Moore’s Law is formulated not just for transistor size and efficiency - it’s also about component cost. Here is the exact definition of Moore’s Law, as proposed by Moore:

The complexity for minimum component costs has increased at a rate of roughly a factor of two per year. Certainly over the short term this rate can be expected to continue, if not to increase. Over the longer term, the rate of increase is a bit more uncertain, although there is no reason to believe it will not remain nearly constant for at least 10 years.

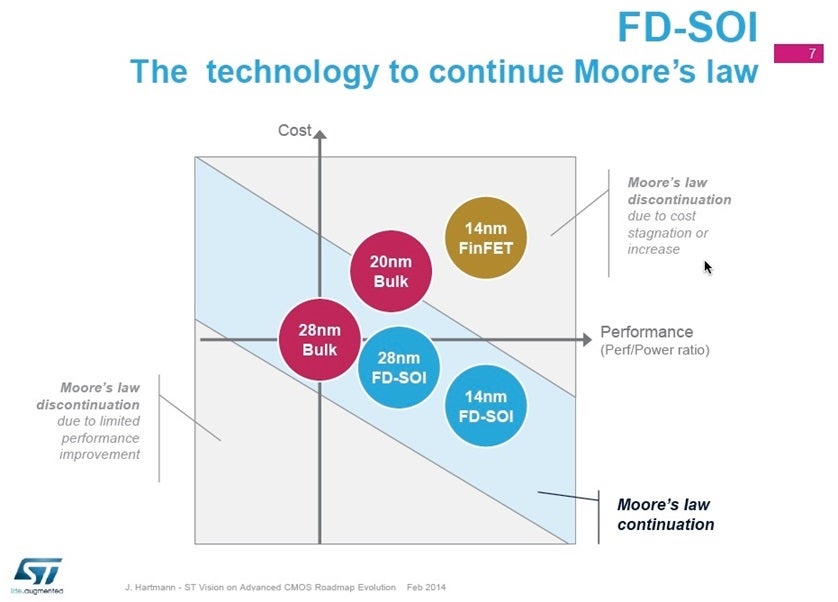

Hearing about the end of Moore's Law around the same time when Intel unveils 14nm Broadwell chips scheduled to come by the end of the year might be strange, but there are plentiful reasons to back up such statement. In order to understand the reasons, you just have to look at the chart below, shown by ST’s Joel Hartmann, showing how cost starts drifting off the vector at 20nm and lower.

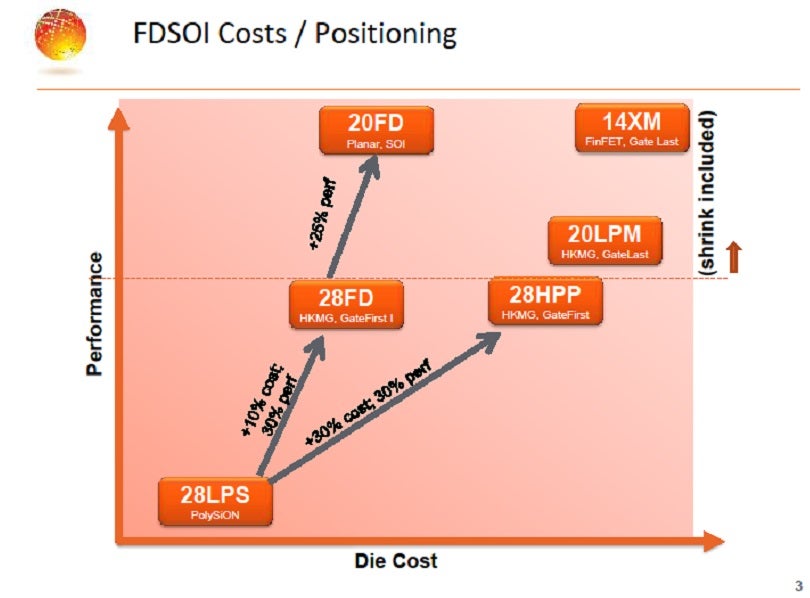

Moreover, this is not an isolated finding: the same data is also backed by chip maker GlobalFoundries, and others. Basically, this second chart by GlobalFoundries shows how 28nm polySiON manufacturing is the most cost efficient architecture at the moment, and scaling down, or using other processes like HKMG and FinFET, comes at a much higher cost ratio.

Gordon Moore formulated the law in 1965

In addition, one has to factor in the increase in wafer prices that zeros out the transistor density gain at sub-28nm nodes. Finally, on top of that, SRAM bit cell size scaling encounters some fundamental challenges at sub 28nm. Since SRAM bit cell size is also crucial for the end SoC size, it is extremely challenging to reduce that size in newer nodes. We recommend you to take a look at the source at the bottom of the article for a detailed breakdown of all the technical difficulties encountered when scaling below 28nm.

However, what seems clear even without digging in much depth is that there are valid reasons why 28nm indeed brings the end of Moore’s Law. This would also bring the end of dimensional scaling that chip makers have relied so long upon. Now, silicon crafters will have to look into different ways to optimize chip performance in the very near future. What would it be? We’re sure we’ll learn soon, but feel free to tell us about your guesses and thoughts right below.

Moore's Law is coming to an end and 28nm seems like its last node

source:

EETimes

Read the latest from Victor Hristov

Things that are NOT allowed:

To help keep our community safe and free from spam, we apply temporary limits to newly created accounts: